In reply to ljepson74:

“Execution of events in the queue may re-trigger an earlier time slot.”,

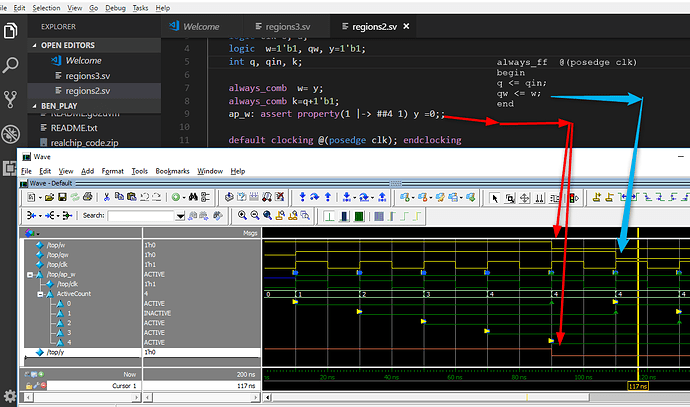

You may be right. From the diagram, an action block may change a variable that is used in a combinational logic (like in always_comb statement. But nonblocking assignments (e.g., a <= b) is evaluated in the Active Region, but does not pick up the 2nd iteration from the action block. consider

module top;

logic clk=0, a;

logic w=1'b1, qw, y=1'b1;

int q, qin, k;

always_comb w= y; // y is updated by the action block at time 90

// qw takes the value of y before the update

// though there is an iteration into th Active region by the action block

ap_w: assert property(1 |-> ##4 1) y =0;;

default clocking @(posedge clk); endclocking

initial forever #10 clk=!clk;

always_ff @(posedge clk) begin

qw <= w;

end

http://SystemVerilog.us/vf/regions2.sv

1800’2017 provides the following regards to simulation regions:

- Figure 4-1—Event scheduling regions

- 4.5 SystemVerilog simulation reference algorithm

My diagram was more of a way to relate design blocks to regions.

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

See Paper: VF Horizons:PAPER: SVA Alternative for Complex Assertions - SystemVerilog - Verification Academy