In reply to katce:

A few comments and observations:

[list=1]

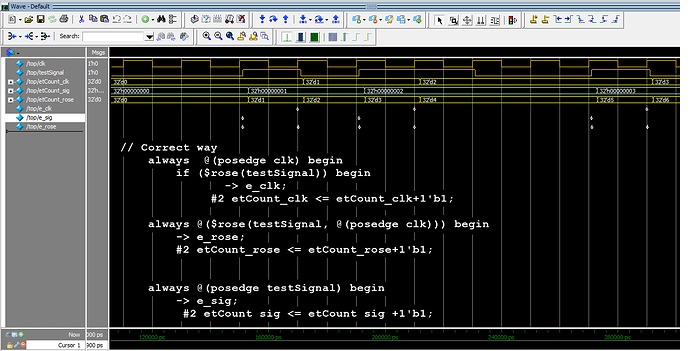

[*] On cover property (##[0:$]rose(testSignal));* You do not need the ##[0:]

[] There is a big difference between always @($rose(testSignal)) and always @(posedge testSignal) and always @(posedge clk) if($rose…

The correct way to code the supporting code is:

// Correct way

always @(posedge clk) begin

if ($rose(testSignal)) begin

-> e_clk;

#2 etCount_clk <= etCount_clk+1'b1;

end

end

Below is an image of the test result that explains the difference. Code is at http://systemverilog.us/vf/explain.sv

image at http://systemverilog.us/vf/explain.png

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

- VF Horizons:PAPER: SVA Alternative for Complex Assertions - SystemVerilog - Verification Academy

- http://systemverilog.us/vf/SolvingComplexUsersAssertions.pdf

- “Using SVA for scoreboarding and TB designs”

http://systemverilog.us/papers/sva4scoreboarding.pdf - “Assertions Instead of FSMs/logic for Scoreboarding and Verification”

https://verificationacademy.com/verification-horizons/october-2013-volume-9-issue-3 - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment

FREE BOOK: Component Design by Example

… A Step-by-Step Process Using VHDL with UART as Vehicle