In reply to Verif Engg:

I have a synchronous FIFO. The depth of the FIFO is 32. Every time the FIFO has 7 or any “n” unique elements inside it, “unique” signal goes HIGH. How do I test the “unique” signal going high in SystemVerilog or UVM? How would my scoreboard look like?

Appreciate any thoughts/ideas.

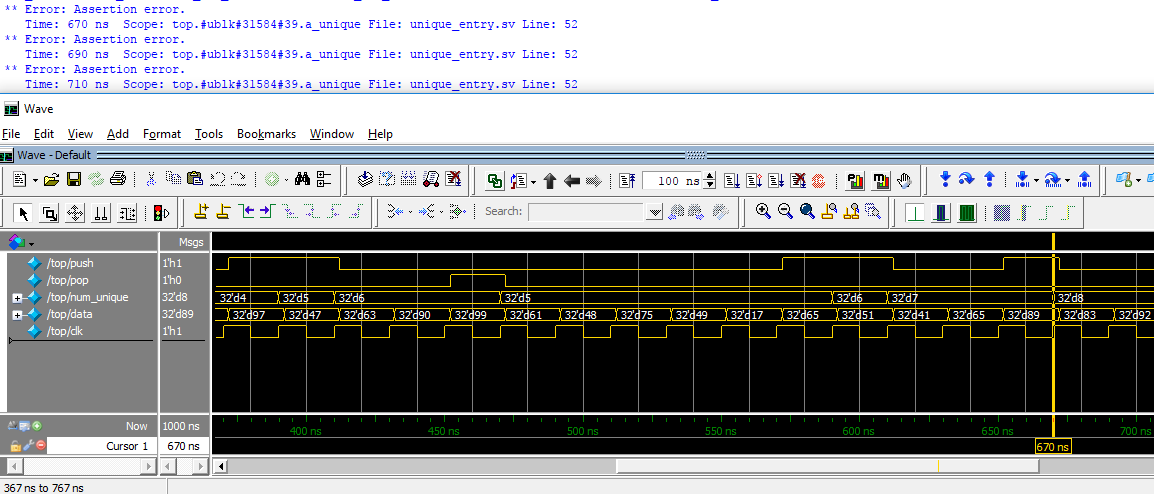

- I am a bit puzzled by the hardware algorithm you used to test the number of unique entries.

- For a testbench, you have the luxury of using associative arrays with interesting methods such as “exists” “num” and “size”

- In the model below, I did use the exists and num.

- I tailored the stimulus vectors to avoid pops on empty queue.

The model(with some lines from 1800’2012 on associative array and queues is at

http://systemverilog.us/vf/unique_entry.sv

// Also see my reply (below) as this model is not complete.

import uvm_pkg::*; `include "uvm_macros.svh"

module top;

bit clk, pop, push;

int data=8;

int aa[int]; // associative array

int q1[$]; // queue, emulating the fifo

int num_unique=0;

always @(posedge clk) begin

automatic int temp_pop;

if(push && !pop)

if(!aa.exists(data)) begin // is unique

aa[data]=1; // flag data into associative array

num_unique <= num_unique+1'b1; // incremnet number of uniques

q1.push_front(data); // maintain the queue

end

if(pop && !push && q1.size != 0) begin

temp_pop=q1.pop_back(); // maintain the queue

num_unique <= num_unique - 1'b1; // decrement uniques

aa.delete(temp_pop); // delete the associative array entry

end

a_unique: assert(aa.num <= 7);

end

initial forever #10 clk=!clk;

initial begin

repeat(5) push <= 1'b1;

repeat(200) begin

@(posedge clk); #2;

if (!randomize(push, pop, data) with

{ push dist {1'b1:=1, 1'b0:=2};

pop dist {1'b1:=1, 1'b0:=8};

data dist {[1:99]:=1, [0:0]:=3};

}) `uvm_error("MYERR", "This is a randomize error")

end

$stop;

end

endmodule

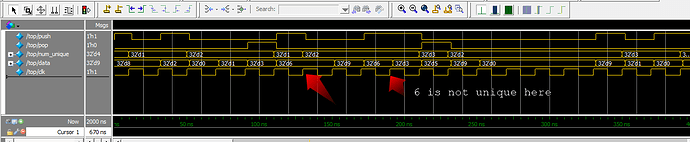

Modifying the data stream with the following constraint

data dist {[1:9]:=1, [0:0]:=3};

causes less unique possibilities.

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact Home - My cvcblr

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115