In reply to yoshiko:

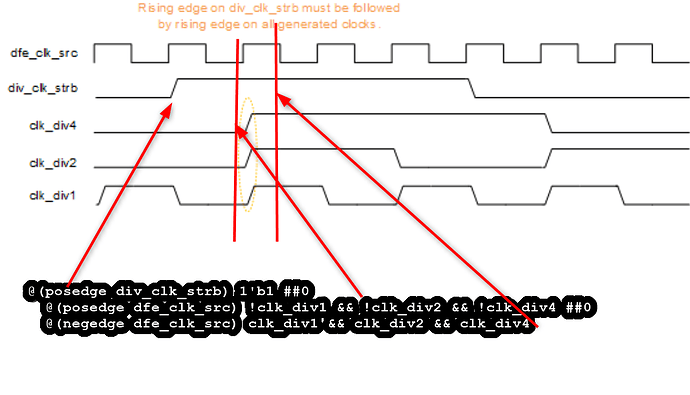

From your timing digram

Following @(posedge div_clk_strb)you want to check that that clk_div1, clk_div2 and clk_div4 signals rose after being clocked by dfe_clk_src. This is how I read you timing diagram.

My assertion states that

- Following @(posedge div_clk_strb)

- at the next @(posedge dfe_clk_src), the sampling values of lk_div1, clk_div2 and clk_div4 are all zeros

- This is then followed that at the next @(negedge dfe_clk_src) the sampling values of lk_div1, clk_div2 and clk_div4 are all ONES

THUS ESSENTIALLY TESTING FOR A ROSE OF THESE 3 SIGNALS.

ap_aligned: assert property(

@(posedge div_clk_strb) 1'b1 ##0

@(posedge dfe_clk_src) !clk_div1 && !clk_div2 && !clk_div4 ##0

@(negedge dfe_clk_src) clk_div1 && clk_div2 && clk_div4 );

You can always create the sampling of these signals using SystemVerilog with the #n delays and test for when they should be all 0’s and all 1’s.

Did I miss something here?

My paper (below) expresses the use of SystemVerilog with tasks to verify complex assertions. Perhaps that paper may give ideas on a different approach.

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

- VF Horizons:PAPER: SVA Alternative for Complex Assertions - SystemVerilog - Verification Academy

- http://systemverilog.us/vf/SolvingComplexUsersAssertions.pdf

- “Using SVA for scoreboarding and TB designs”

http://systemverilog.us/papers/sva4scoreboarding.pdf - “Assertions Instead of FSMs/logic for Scoreboarding and Verification”

https://verificationacademy.com/verification-horizons/october-2013-volume-9-issue-3 - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment