In reply to bdreku:

Could u please explain a difference of BFM and VIP?

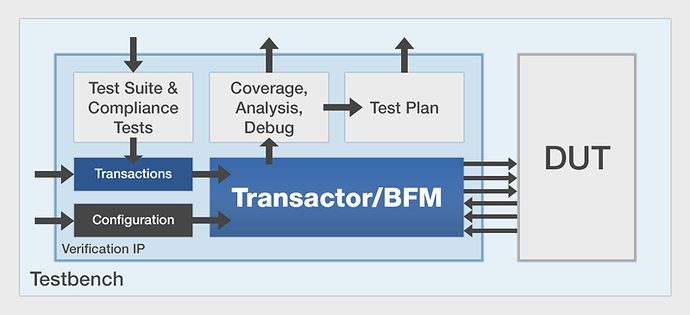

I am not sure, but as per my understanding, VIP = scenario generator + BFM

This site provides a good explanation and shows the architecture of a VIP

If you look at

you’ll see that a BFM is a model of the interface to the DUT. The VIP includes, besides the BFM, the test environment to allow the user to integrate his DUT and verify that the DUT’s interface (e,g,Ethernet) does meet the specs for that bus. If you don’t have a packaged VIP, then you would have to create one yourself. Specifically, you would need to fully understand the interface, define a test plan, write a test suite, define a BFM that accepts the commanded transactions (e.g., read/writes) and responds to the DUT. You must also provide the verification that the DUT does indeed meet the interface requirement per specs (e.g., the Ethernet spec). It is a LOT OF WORK! For standard protocols, buying a VIP is faster, and could even be cost effective.

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SystemVerilog Assertions Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115