In reply to lisa.lalice:

Works for me!

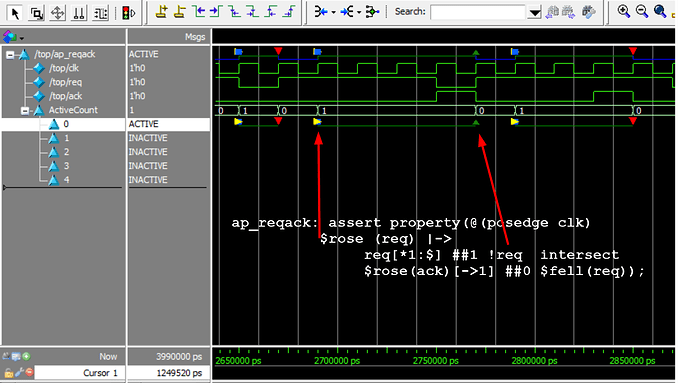

ap_reqack: assert property(@(posedge clk)

$rose (req) |->

req[*1:$] ##1 !req intersect

$rose(ack)[->1] ##0 $fell(req));

module top;

timeunit 1ns/10ps;

`include "uvm_macros.svh"

import uvm_pkg::*;

bit clk, req, ack;

initial forever #10 clk=!clk;

ap_reqack: assert property(@(posedge clk)

$rose (req) |->

req[*1:$] ##1 !req intersect

$rose(ack)[->1] ##0 $fell(req));

initial begin

repeat(200) begin

@(posedge clk);

if (!randomize(req, ack) with

{ req dist {1'b1:=5, 1'b0:=1};

ack dist {1'b1:=1, 1'b0:=5};

}) `uvm_error("MYERR", "This is a randomize error");

end

$finish;

end

endmodule