In reply to lisa.lalice:

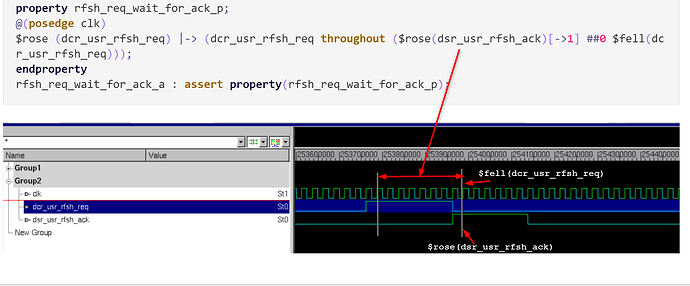

Your assertion does not meet the waveform you display

(dcr_usr_rfsh_req throughout ($rose(dsr_usr_rfsh_ack)[->1] ##0 $fell(dcr_usr_rfsh_req)));

If you want anassertion to meet your waveform where dcr_usr_rfsh_req==0 when

$rose(dsr_usr_rfsh_ack)==1 then do the following:

$rose (dcr_usr_rfsh_req) |->

(dcr_usr_rfsh_req[*1:$] ##1 !dcr_usr_rfsh_req intersect

($rose(dsr_usr_rfsh_ack)[->1] ##0 $fell(dcr_usr_rfsh_req)));

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home.html

** SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

…

- SVA Package: Dynamic and range delays and repeats SVA: Package for dynamic and range delays and repeats - SystemVerilog - Verification Academy

- Free books: Component Design by Example https://rb.gy/9tcbhl

Real Chip Design and Verification Using Verilog and VHDL($3) Amazon.com - Papers:

- Understanding the SVA Engine,

Verification Horizons - SVA Alternative for Complex Assertions

https://verificationacademy.com/news/verification-horizons-march-2018-issue - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment