HI All,

I am writing an assumption for the following requirement;

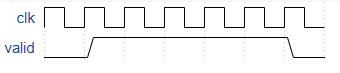

valid is an input signal. I want to constraint/write assume, once it goes HIGH, it should remain HIGH for at least 6 clock cycles and then it should go low.

I have written like this;

assume property (

@(posedge clk)

//$rose(valid) |-> ##[6:8] !valid; //case_1

$rose(valid) |-> ##[6:8] $fell(valid)

); //case_2

endproperty

both cases are not working as expected. After running this,

cover precodnition (antecedent) is getting passed,

but cover witness is getting undermined.

Result : property is keep running, looks like some issue.

Could you please suggest what could be wrong here?