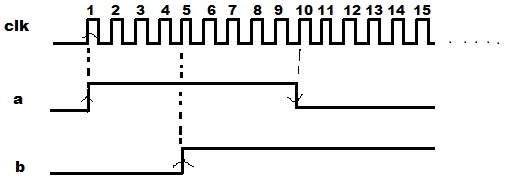

Q. Whenever sig_a rises, after 5 clk cycles sig_b should be high and it will be stable with sig_a for 5 clk cycles later sig_a will be low

Here You have to check for the first thing is about that when you want to check your design using assertion w.r.t. clk or etc? Then check the conditions as you said first a then after 5 clk cycle b should be check !..

module tb;

bit clk, a,b ;

always #2 clk = ~clk;

sequence seq;

a ##5 b;

endsequence

property prop;

@(posedge clk) seq;

endproperty

logical_exp: assert property(prop) else $error("ASSERTION FAILED at T = %0t",$time);

initial begin

@(posedge clk)

a = 1;

#16 b = 1;

#20 a = 0;

#20; $finish;

end

initial begin

$dumpfile("dump.vcd");

$dumpvars;

end

endmodule

/* Q. Whenever sig_a rises, after 5 clk cycles sig_b should be high

and it will be stable with sig_a for 5 clk cycles later sig_a will be low */

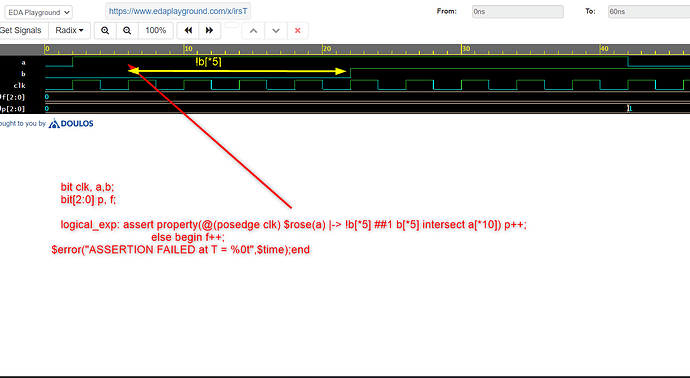

module tb;

bit clk, a,b;

bit[2:0] p, f;

always #2 clk = !clk;

logical_exp: assert property(@(posedge clk) $rose(a) |-> !b[*5] ##1 b[*5] intersect a[*10]) p++;

else begin f++; $error("ASSERTION FAILED at T = %0t",$time);end

initial begin

@(posedge clk)

a <= 1;

repeat(5) @(posedge clk);

b <= 1;

repeat(5) @(posedge clk);

a <= 0;

#20; $finish;

end

initial begin

$dumpfile("dump.vcd");

$dumpvars;

end

endmodule

Thank you @user49

Q: Does this check if sig_a will be low after 5 clks?

NO, but one could either add another assertion or modify this to something like:

assert property(@(posedge clk)

$rose(a) |-> (!b[*5] ##1 b[*5] intersect a[*10]) ##1 $fell(a));

// Note the ()

it all depends on the requirements. If that fell is important, then you can add that. I assumed it was not. But again, this exercise and the use of assertions demonstrate how requirements are clarified.