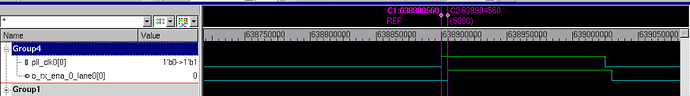

I want to do an assertion check where signal B must high 5000s after signal A is high.

I tried this code but I got an error regarding “multi-clock overlapping”

property Check_RXENA;

realtime start;

@(posedge pll_clk0)

if((clksel == 0) && (txsel ==0))

(@(posedge pll_clk0) (1,start=$realtime) ##0 @(posedge rx_ena) $realtime-start==5000);

endproperty

May I know if there is other suitable approach on how to do this?

ben2

2

In reply to lisa.lalice:

I would have written your assertion this way.

module top;

timeunit 1ns; timeprecision 100ps;

bit pll_clk0, clksel, txsel, rx_ena;

property Check_RXENA;

realtime start;

@(posedge pll_clk0)

(clksel == 0 && txsel ==0, start=$realtime) |->

@(posedge rx_ena) $realtime-start==5000;

endproperty

ap: assert property(Check_RXENA);

endmodule

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home.html

** SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

…

- SVA Package: Dynamic and range delays and repeats SVA: Package for dynamic and range delays and repeats | Verification Academy

- Free books: Component Design by Example FREE BOOK: Component Design by Example … A Step-by-Step Process Using VHDL with UART as Vehicle | Verification Academy

Real Chip Design and Verification Using Verilog and VHDL($3) https://rb.gy/cwy7nb

- Papers: