Here is my simple design of synchronous fifo:

module sync_fifo #(parameter DEPTH = 8, WIDTH = 16) (

input bit clk,

rst_n,

rd_en,

wr_en,

input logic [WIDTH-1 : 0] data_in,

output logic [WIDTH-1 : 0] data_out,

output bit full,

empty

);

logic [$clog2(DEPTH)-1 : 0] rd_ptr;

logic [$clog2(DEPTH)-1 : 0] wr_ptr;

logic [WIDTH-1 : 0] fifo[DEPTH-1 : 0];

logic [$clog2(DEPTH)-1:0]count;

always@(posedge clk) begin

$display($time,"[DUT] wr-en = %0d",wr_en);

end

always_ff @(posedge clk) begin

if(!rst_n) begin

wr_ptr <=0;

end

else begin

if(wr_en && !full) begin

fifo[wr_ptr] <= data_in;

wr_ptr <= wr_ptr +1;

end

else $display("[DUT] write failed");

end

end

always_ff @(posedge clk) begin

if(!rst_n) begin

rd_ptr <= 0;

end

else begin

if(rd_en && !empty) begin

data_out <= fifo[rd_ptr];

rd_ptr <= rd_ptr +1;

end

end

end

always_ff @(posedge clk) begin

if(!rst_n) begin

count <= 0;

end

else begin

case({wr_en,rd_en})

2'b10 : count <= count + 1;

2'b01 : count <= count - 1;

default : count <= count;

endcase

end

end

assign empty = (count == 0) ? 1'b1 : 1'b0;

assign full = (DEPTH == count) ? 1'b1 : 1'b0;

endmodule

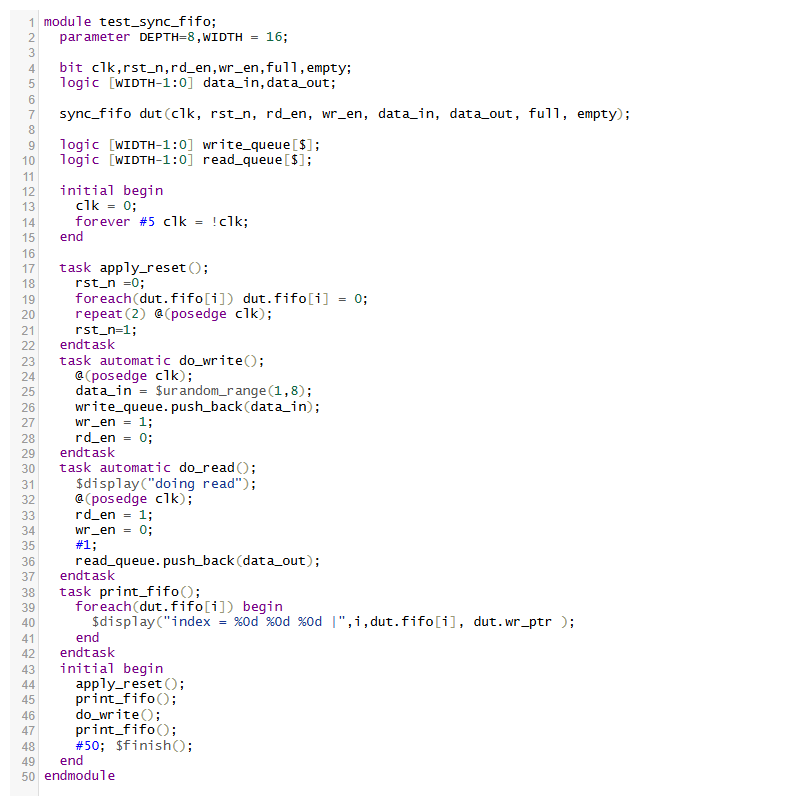

I wrote a simple testbench to verify it :

But the write operation is not performing as desired . Could someone please explain what’s happening?