In reply to Jung Ik Moon:

- The “not” operator is a property operator and is not a sequence operator.

Thus, the following is incorrect.

##1 (not (my_seq), t = t - 1)[*0:$] - If the consequent has a infinite delay range it can never fail; it can succeed

a |-> ##[1:$] b; // same as

a |-> ##1 b or ##2 b or ##3 b or ... ##n b; // can never fail

//

a |-> ##1 (1, t = t - 1)[*0:$] ##1 c; // is same as

a |-> ##1 c or ((1, t = t - 1)[*1] ##1 c) or ((1, t = t - 1)[*2] ##1 c) or ..

// Thus, can never fail

//

a |-> ##1 (b, t = t - 1)[*0:$] ##1 c; // is same as

a |-> ##1 c or ((b, t = t - 1)[*1] ##1 c) or ((b, t = t - 1)[*2] ##1 c) or ..

// This CAN fail because a sequence of " b==1 ##1 b==0" fails the b[*2], and would also fail the b[*3] and etc.

- The use of not of a sequence can be confusing. Why not making it a positive type of requirement. Thus instead of [list]

- “my_seq to my_seq delay should not be less than my_timing.”, use

- “my_seq to my_seq delay should be >= than my_timing.”

[*] You need the **first_match()**operator to get a failure.

[/list]

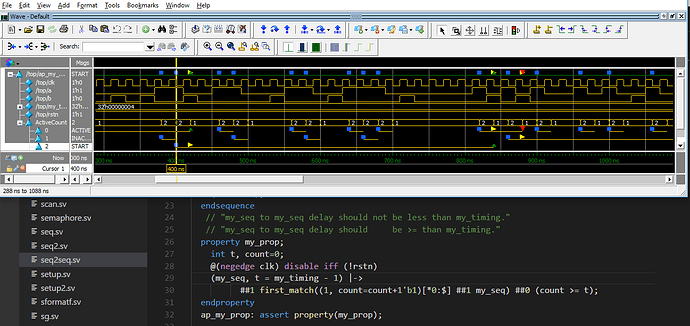

Below is code, link to the test file, and the simulation results.

int my_timing= 4;

sequence my_seq;

( a ##1 b);

endsequence

// "my_seq to my_seq delay should not be less than my_timing."

// "my_seq to my_seq delay should be >= than my_timing."

property my_prop;

int t, count=0;

@(negedge clk) disable iff (!rstn)

(my_seq, t = my_timing -1 ) |-> // ** Don't need the "-1", was a copy/paste mistake

##1 first_match((1, count=count+1'b1)[*0:$] ##1 my_seq) ##0 (count >= t);

endproperty

ap_my_prop: assert property(my_prop);

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115