I have a 2x1 mux as DUT which I am trying to verify using two concurrent processes as a learning exercise.

My two processes look like this:

initial begin : apply_tests

for (int i = 0; i < 8; i++) begin

in0 <= i[0];

in1 <= i[1];

sel <= i[2];

@(posedge clk);

end

$stop;

end

initial begin : monitor_signals

forever begin

@(posedge clk);

correct_out = sel ? in1 : in0;

if (correct_out != out) begin

// some $display and $error statement here

end

end

end

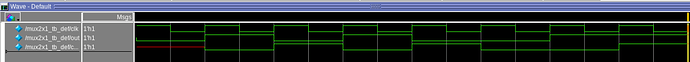

I see the following waveform:

I have the following questions:

- It seems, from the waveform that

correct_outis trailingoutby one cycle. Yet, theifblock in the monitor_signals process is never triggered (I know that because the $display statements never get printed). Why is that? - Secondly, if I move the (@posedge clk) after the

ifblock in the second process, that seems to have no impact on the output waveform or the simulation output. Is it correct, then, to infer that positioning of event control statements within a procedural process block (e.g. initial, always etc.) do not matter? That is, regardless of the positioning of the event control statement, sampling of values will always happen at the same time?

Thanks in advance.