Q. For below code I an getting error at @25 without check complete sequnce how tool can through error?

`timescale 1ns/1ps

module axi_awaddr_assertion_tb;

// Signals

logic clk;

logic rst_n;

logic awvalid;

logic awready;

logic \[31:0\] awaddr;

// Clock generation

initial clk = 0;

always #5 clk = \~clk; // 100 MHz clock

// Reset and stimulus

initial begin

rst_n = 0;

awvalid = 0;

awready = 0;

awaddr = 32’h0;

#20;

rst_n = 1;

end

initial begin

@(posedge rst_n);

// VALID AXI behavior (PASS)

// ---

@(posedge clk);

awvalid = 1;

awaddr = 32'hDEADBEEF;

// Hold address stable while AWREADY = 0

repeat (3) @(posedge clk);

awready = 1; // Handshake

@(posedge clk);

awvalid = 0;

awready = 0;

// ---

// INVALID AXI behavior (to see FAIL)

// ---

@(posedge clk);

awvalid = 1;

awaddr = 32'hAAAA5555;

@(posedge clk);

awaddr = 32'hBBBB6666; // ILLEGAL CHANGE - should fail assertion

@(posedge clk);

awready = 1;

#50;

$finish;

end

// —

// AXI ASSERTION

// —

property awaddr_stable_when_valid;

@(posedge clk)

disable iff (!rst_n)

(awvalid && !awready) ##1(awaddr);

endproperty

// Assertion instance

assert property (awaddr_stable_when_valid)

else $error(“AXI AWADDR changed while AWVALID=1 and AWREADY=0”);

// Waveform dumping

initial begin

$dumpfile(“wave.vcd”);

$dumpvars();

end

endmodule

/*

axi_awaddr_assertion_tb

Loading snapshot worklib.axi_awaddr_assertion_tb:sv … Done

xcelium> source /xcelium23.09/tools/xcelium/files/xmsimrc

xcelium> run

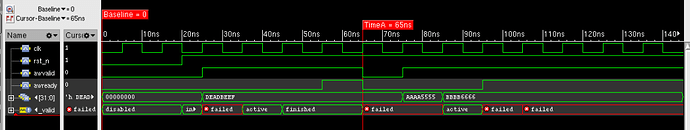

xmsim: *E,ASRTST (./testbench.sv,73): (time 25 NS) Assertion axi_awaddr_assertion_tb.awaddr_stable_when_valid has failed

AXI AWADDR changed while AWVALID=1 and AWREADY=0

xmsim: *E,ASRTST (./testbench.sv,73): (time 65 NS) Assertion axi_awaddr_assertion_tb.awaddr_stable_when_valid has failed

AXI AWADDR changed while AWVALID=1 and AWREADY=0

xmsim: *E,ASRTST (./testbench.sv,73): (time 75 NS) Assertion axi_awaddr_assertion_tb.awaddr_stable_when_valid has failed

AXI AWADDR changed while AWVALID=1 and AWREADY=0

xmsim: *E,ASRTST (./testbench.sv,73): (time 105 NS) Assertion axi_awaddr_assertion_tb.awaddr_stable_when_valid has failed

AXI AWADDR changed while AWVALID=1 and AWREADY=0

xmsim: *E,ASRTST (./testbench.sv,73): (time 115 NS) Assertion axi_awaddr_assertion_tb.awaddr_stable_when_valid has failed

AXI AWADDR changed while AWVALID=1 and AWREADY=0

xmsim: *E,ASRTST (./testbench.sv,73): (time 125 NS) Assertion axi_awaddr_assertion_tb.awaddr_stable_when_valid has failed

AXI AWADDR changed while AWVALID=1 and AWREADY=0

xmsim: *E,ASRTST (./testbench.sv,73): (time 135 NS) Assertion axi_awaddr_assertion_tb.awaddr_stable_when_valid has failed

AXI AWADDR changed while AWVALID=1 and AWREADY=0

Simulation complete via $finish(1) at time 145 NS + 0

./testbench.sv:59 $finish;

xcelium> exit

TOOL: xrun 23.09-s001: Exiting on Dec 27, 2025 at 04:47:31 EST (total: 00:00:01)

Exit code expected: 0, received: 1

*/