The 100ps is a hold time, and has no effect on the assertion.

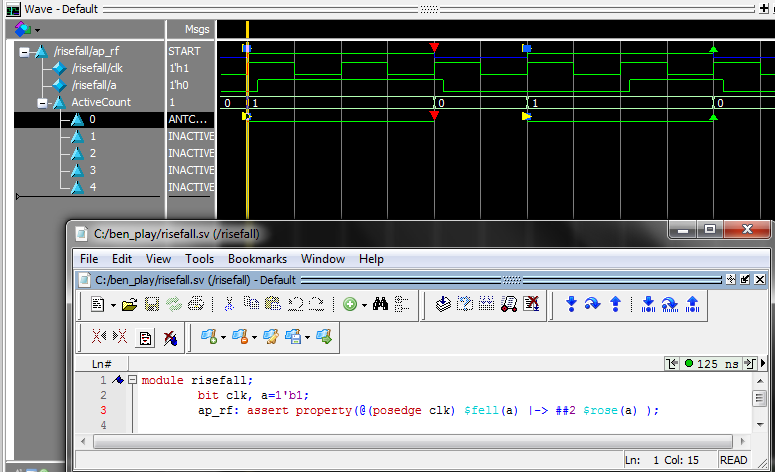

What you have as an assertion is correct. Below is a simple model, with a hold time (though not needed) along with the simulation results. It works as expected.

module risefall;

bit clk, a=1'b1;

ap_rf: assert property(@(posedge clk) $fell(a) |-> ##2 $rose(a) );

initial forever #5 clk=!clk;

initial begin

@(posedge clk);

repeat(200) begin

@(posedge clk);

#1;

if (!randomize(a)) $error();

end

end

endmodule

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SystemVerilog Assertions Handbook 3rd Edition, 2013 ISBN 878-0-9705394-3-6

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115