Hi All,

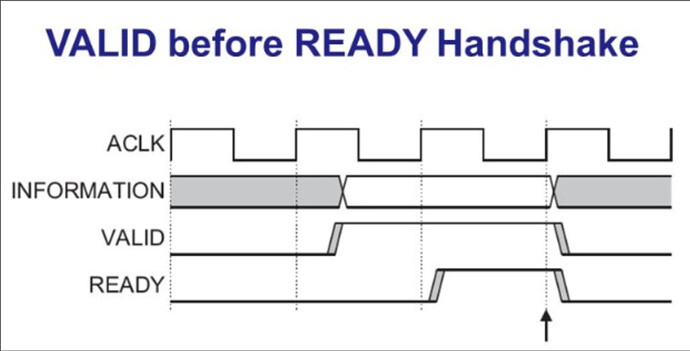

I am trying to write Driver for the following scenario where Valid and Information could be driven between two posedges of clock

Generally we write driver as

forever begin

seq_item_port.get(req);

// @(posedge vif.ACLK); // (Q1) Is this Required ?

// Assume that 'req' type has 'delay' random property with it's own constraint

if( req.get_delay() > 0 ) begin

req.get_delay()*1ps;

end

vif.VALID <= 1'b1;

vif.INFO <= req.info;

wait( $rose(vif.VALID & vif.READY,@(posedge vif.ACLK) );

// Unblocks when handshake occurs

vif.VALID <= 1'b0;

// Collect Response and Data for Reads. Driver would call put_response after that

end

(Q1) Once get unblocks, are there any advantages of waiting for the nearest posedge of clock ?

(Q2) If Ready were asserted before Valid is driven then would we ever observe Valid being asserted or would it be overridden with 2nd NBA ( with value as 0 thereby never seeing it’s assertion ) ?

Regards