In reply to sudharshan:

b[->2] // is equivalent to:

!b[*0:$] ##1 b ##1 !b[*0:$] ##1 b

// In other words any two "b"s ending with a "b"

b[=2] // is equivalent to:

!b[*0:$] ##1 b ##1 !b[*0:$] ##1 b ##1 !b[*0:$]

// In other words any two "b"s not necessarily ending with a "b",

// could be NO "b"s after the last "b"

// Thus, what you need is

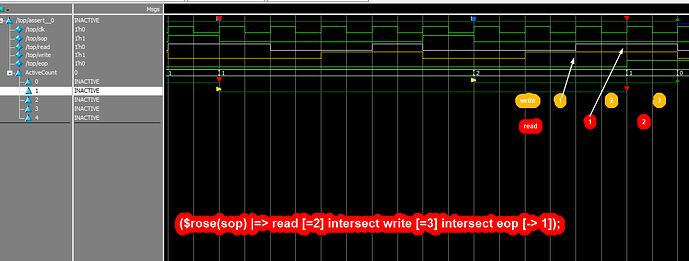

assert property ($rose(sop) |=> read [=2] intersect write [=3] intersect eop [-> 1]);

http://SystemVerilog.us/vf/intersect1.sv

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

- SVA Alternative for Complex Assertions

Browse all content in Verification Academy: Articles, Cookbooks, Resources, Sessions, and Tracks - SVA: Package for dynamic and range delays and repeats - SystemVerilog - Verification Academy

- SVA in a UVM Class-based Environment

SVA in a UVM Class-based Environment