module modulation (

input logic clk,

input logic reset,

input logic enable,

input logic input1,

input logic ready, // Handshake signal: Ready from downstream

output logic signed [15:0] output1,

output logic signed [15:0] output2,

output logic valid

);

// Internal signals

logic [2:0] counter;

logic [1:0] b;

logic signed [15:0] seven = 16'h5A82;

logic signed [15:0] seven_negative = 16'hA57E;

typedef enum logic [1:0] {IDLE, LOAD, PROCESS, DONE} state_t;

state_t current_state, next_state;

// Sequential logic: State and counter

always_ff @(posedge clk or posedge reset) begin

if (reset) begin

current_state <= IDLE;

counter <= 3'b000;

b <= 2'b00;

end else begin

current_state <= next_state;

if (current_state == LOAD && enable) begin

counter <= (counter == 3'b010) ? 3'b000 : counter + 1;

b <= {b[0], input1};

end

end

end

// Next state logic (FSM)

always_comb begin

next_state = current_state; // Default to current state

case (current_state)

IDLE:

if (enable) next_state = LOAD;

LOAD:

if (counter == 3'b010) next_state = PROCESS;

PROCESS:

if (ready) next_state = DONE;

DONE:

next_state = IDLE; // Return to idle after completion

default:

next_state = IDLE;

endcase

end

// Output logic and handshake

always_comb begin

valid = 1'b0;

output1 = '0;

output2 = '0;

if (current_state == PROCESS) begin

valid = 1'b1; // Signal that output is valid

case (b)

2'b00: begin

output1 = seven;

output2 = seven;

end

2'b01: begin

output1 = seven;

output2 = seven_negative;

end

2'b10: begin

output1 = seven_negative;

output2 = seven;

end

2'b11: begin

output1 = seven_negative;

output2 = seven_negative;

end

default: begin

output1 = '0;

output2 = '0;

end

endcase

end

end

endmodule

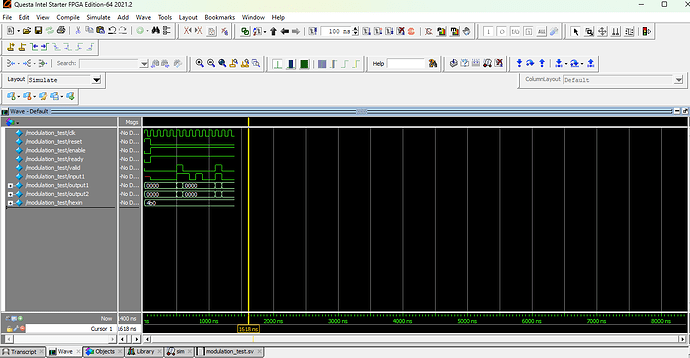

module modulation_test;

// Declare signals

logic clk;

logic reset;

logic enable;

logic ready;

logic valid;

logic input1;

logic signed [15:0] output1;

logic signed [15:0] output2;

logic [11:0] hexin;

// Initialize the hexin signal

initial hexin = 12'h4B0;

// Instantiate the DUT

modulation dut (

.clk(clk),

.reset(reset),

.enable(enable),

.input1(input1),

.output1(output1),

.output2(output2),

.ready(ready),

.valid(valid)

);

// Clock generation

initial clk = 1'b1;

always #50 clk = ~clk; // 50 MHz clock

// Stimulus process

initial begin

reset = 1'b1;

enable = 1'b0;

ready = 1'b0;

#100;

reset = 1'b0;

enable = 1'b1;

for (int i = 0; i < 12; i++) begin

input1 = hexin[i];

ready = 1'b1; // Simulate ready signal

#100;

end

// End simulation

#100;

$finish;

end

endmodule

i have no clue how i can fix, i am new at this program.