In reply to Monarch Dave:

SVA does not allow the access of local variables from the action block.

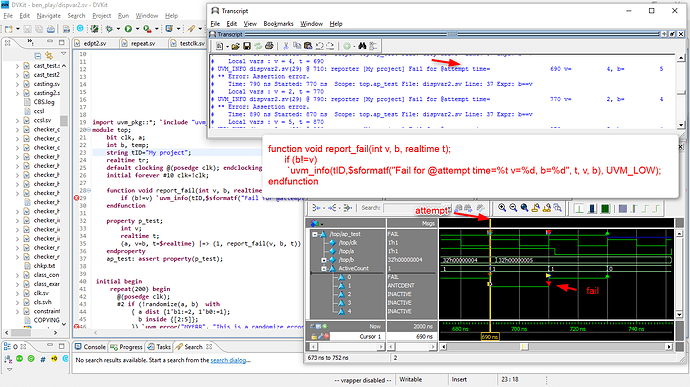

Some simulators do report the value of the variables upon a failure. However, if you absolutely want to have access you can do what I have in the example below. In this example,

the property is

(a, v=b, t=$realtime) |=> (b==v); // where b and v are int.

import uvm_pkg::*; `include "uvm_macros.svh"

module top;

bit clk, a;

int b, temp;

string tID="My project";

realtime tr;

default clocking @(posedge clk); endclocking

initial forever #10 clk=!clk;

function void report_fail(int v, b, realtime t);

if (b!=v)

`uvm_info(tID,$sformatf("Fail for @attempt time=%t v=%d, b=%d", t, v, b), UVM_LOW);

endfunction

property p_test;

int v;

realtime t;

(a, v=b, t=$realtime) |=> (1, report_fail(v, b, t)) ##0 (b==v);

endproperty

ap_test: assert property(p_test);

initial begin

repeat(200) begin

@(posedge clk);

#2 if (!randomize(a, b) with

{ a dist {1'b1:=2, 1'b0:=1};

b inside {[2:5]};

}) `uvm_error("MYERR", "This is a randomize error")

end

$finish;

end

endmodule

you can change the UVM verbosity with th ewneeded verbosity with:

simulation_command +UVM_VERBOSITY=UVM_HIGH filename.sv

Code file: http://systemverilog.us/vdispvar2.sv

Results

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

// For 10% discount, use code 45KJT5GN @ https://www.createspace.com/5810350 - A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115