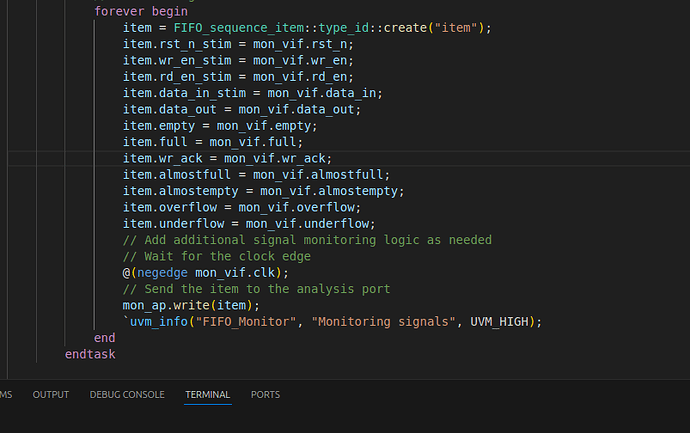

i was working on FIFO UVM and was driving and monitoring at negedge and my scoreboard was giving me that the output is correct but when I changed the driver and monitor to work with @posedge the scoreboard showed that the output captured with monitor is delayed 1 clk cycle from the out_ref of the scoreboard

If the DUT and testbench both use @posedege, you have a race condition if your assignments are blocking. Your testbench needs to use non-blocking assignments <= if you want them synchronized to the same edge.

thank you for your response.

i tried to make it nonblocking but it still gives me the same behaviour.

will clocking block solve it?

- is it right to drive at negedge to avoid such race conditions or it is standard to drive and monitor at posedge

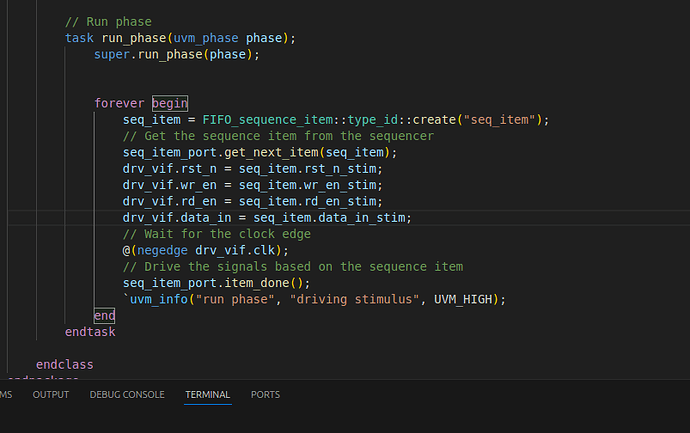

Hard to say without seeing exactly how your DUT signals are being driven. And usually the @() event control is at the top of the forever loop, not in the middle of it. And you would use try_next_item()

forever @(posedge clk)

if (try_next_item(req)) begin

// drive interface

seq_item_port.item_done(req);

end

1 Like