In reply to ben@SystemVerilog.us:

Thanks. We are going to start trying to work these in, in bits and pieces. Starting… with a couple of serial transmitters. About your paper, Assertions Instead of FSMs/logic for Scoreboarding and Verification, a couple of questions.

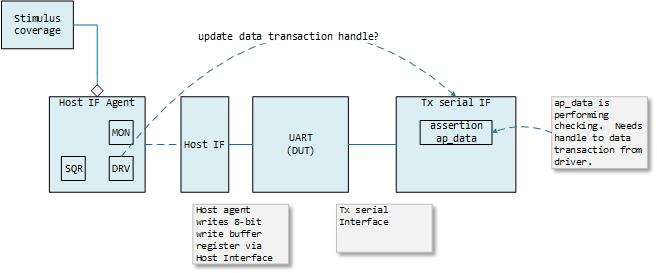

I’ve drawn up how I interpreted the paper into a picture. When you explain the steps, you write “For the next 8 cycles, serial data is collected and verified on a bit-by-bit basis against expected data. That expected data is the sent_data from the driver, which is a synchronous copy of item_h.data, where item_h is the handle in the DUT interface, and data is the data word written to the DUT that gets serialized and sent by the DUT. That handle is updated from the driver.”

In application, the driver is on the other side of the DUT, in the parallel loading interface writing the Tx buffer. How is this driver updating the other (tx serial) interface’s transaction handle (which contains the data loaded into the Tx Buffer). Aka does this driver have VIF to a different interface? That seems like an unwanted dependency.

My “host If” is just like the “APB” interface from the UART example in the mentor coverage cookbook on pg 52. With your setup, you don’t need the scoreboard, or the passive agent. Anyway.