In reply to bmorris:

I’ve got a VHDL DUT, with an interface which talks to a chip on the PLB. In order to simulate my DUT in a UVM environment, I’ll need a model of this external chip. Should I write a new VHDL component which mimics the behavior of the chip?

Also, I developed a transaction based SV model of the DUT (my golden model); do I also need to create a SV model of the chip for the golden model to talk to, or do they somehow share the one model. #Confused

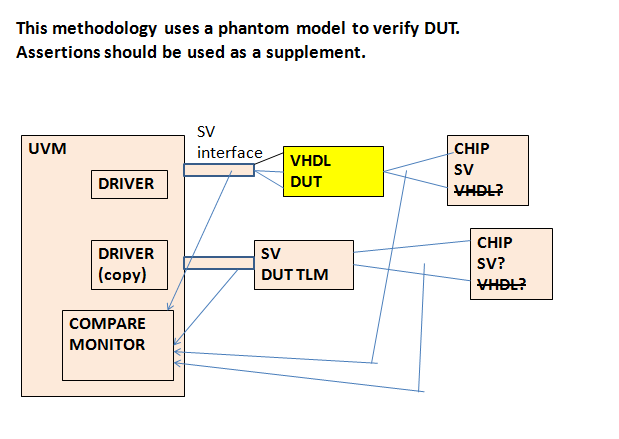

I drew a couple of diagrams to better understand the issues. The way you describe the verification environment, it seems that you are using a phantom model of the DUT and chip as the “golden copy”, and then do a compare between the the DUT/CHIP set and the golden SV/CHIP set. I show this here

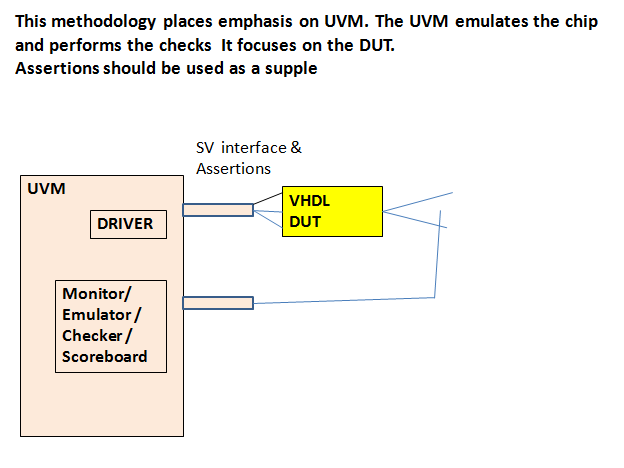

Another approach would be to just use the VHDL DUT in a UVM environment, and let in the UVM environment, a checker that may (not sure if this is really needed, but maybe) emulate the main characteristics of the chip. I show this here

I prefer this 2nd solution because it put all the emphasis on verifying the DUT. I also recommend, in either approach, the ddition of SystemVerilog assertions.

However, you reall need to evaluate the complexity of each of those solutions, but my vote in on the 2nd one. Others, please put your 2 cents in.

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115