In reply to shivamdec:

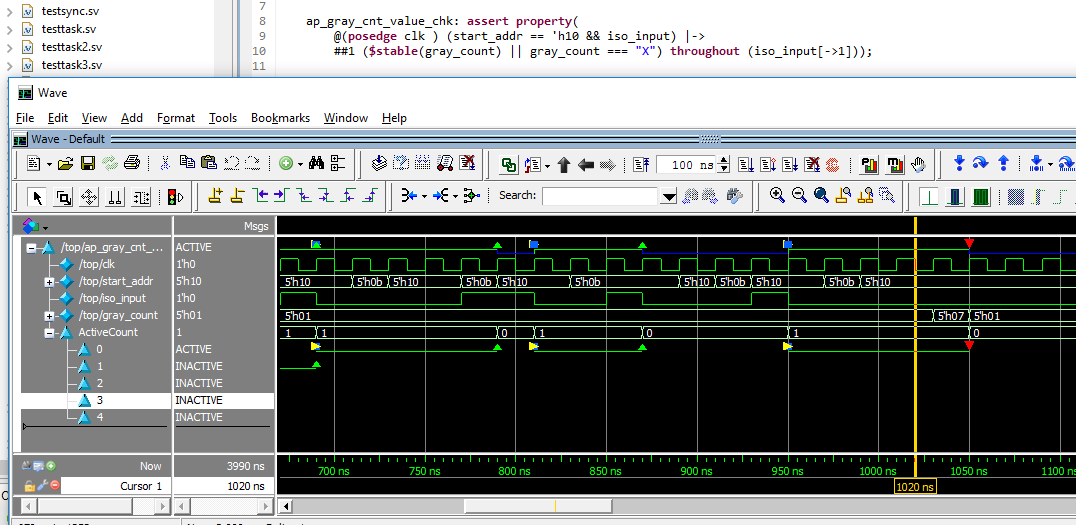

My mistake on the troughout, see updated code below and sim results.

On [->0], that does not make sense.

b [->m] is equivalent to ( !b [*0:] ##1 b)[*m]

Thus, b[->0] is same as (!b[*0:] ##1 b)[*0] , and that is empty

import uvm_pkg::*; `include "uvm_macros.svh"

module top;

bit clk, a, b, iso_input;

logic[4:0] start_addr, gray_count;

default clocking @(posedge clk); endclocking

initial forever #10 clk=!clk;

ap_gray_cnt_value_chk: assert property(

@(posedge clk ) (start_addr == 'h10 && iso_input) |->

##1 ($stable(gray_count) || gray_count === "X") throughout (iso_input[->1]));

initial begin

repeat(200) begin

@(posedge clk);

if (!randomize(start_addr, iso_input, gray_count) with

{ start_addr dist {5'b10000:=3, 5'b01011:=1};

gray_count dist {3'b1:=101, 3'b111:=2};

iso_input dist {1'b0:=3, 1'b1:=1};

}) `uvm_error("MYERR", "This is a randomize error")

end

$stop;

end

endmodule

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115