In reply to pvpatel:

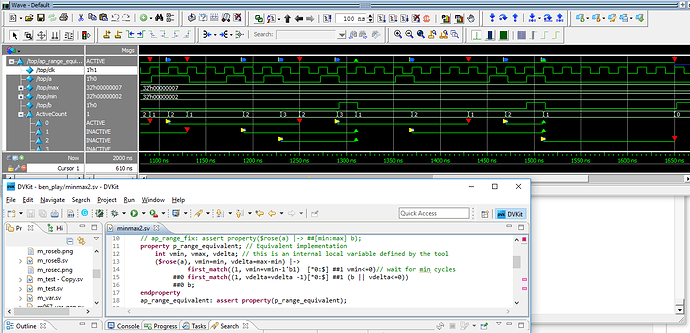

The following is a variation of a model in my SVA Handbook 4th Edition, 2016 Code is also at http://SystemVerilog.us/vf/minmax2.sv

// $rose(a) |-> ##[min:max] (b == 1); //Error

import uvm_pkg::*; `include "uvm_macros.svh"

module top;

bit clk, a, b;

int min=2, max=7, thread;

default clocking @(posedge clk); endclocking

initial forever #10 clk=!clk;

// ap_range_fix: assert property($rose(a) |-> ##[min:max] b);

property p_range_equivalent; // Equivalent implementation

int vmin, vmax, vdelta; // this is an internal local variable defined by the tool

($rose(a), vmin=min, vdelta=max-min) |->

first_match((1, vmin=vmin-1'b1) [*0:$] ##1 vmin<=0)// wait for min cycles

##0 first_match((1, vdelta=vdelta -1)[*0:$] ##1 (b || vdelta<=0))

##0 b; // test for b in case above finished because vdelta <=0

endproperty

ap_range_equivalent: assert property(p_range_equivalent);

initial begin

repeat(100) begin

@(posedge clk);

#2 if (!randomize(a, b) with

{ a dist {1'b1:=1, 1'b0:=6};

b dist {1'b1:=1, 1'b0:=11};

}) `uvm_error("MYERR", "This is a randomize error")

end

repeat(100) begin

@(posedge clk);

#2 if (!randomize(a, b) with

{ a dist {1'b1:=1, 1'b0:=6};

b dist {1'b1:=1, 1'b0:=1};

}) `uvm_error("MYERR", "This is a randomize error")

end

$stop;

end

endmodule

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115