Hi, I am new to AHB Protocol. I have two questions, can someone please help to clarify this:

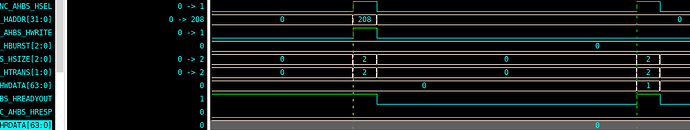

- If we have haddr(0xA), hwrite(1), hsel(1) and hready(1), then if hready goes low in the next cycle, does hwdata needs to be valid from this time until hready is 1 again or it can be change to the valid value in same clock cycle when hready goes high? Basically, what we call data phase has to be necessarily starting in next cycle or it can have some delay. Attaching waveform for reference.

- If we have just a single write, then does it matter if we keep sel as 1/0 during the data phase ? If yes, how do we differ between the read transfer address phase and write transfer data phase because hwrite and other control signals are same for both cases.