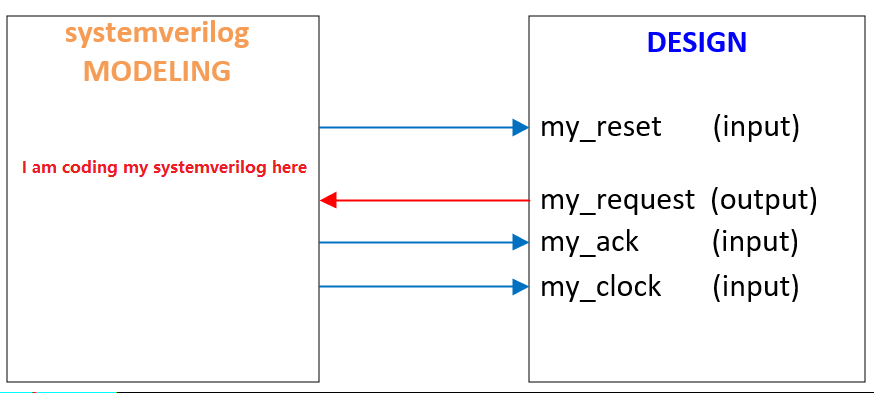

I am trying to model clock, request and ack handshake behavior.

Design sends out request in order to obtain an input clock.

there are ack & reset ports in the design as well.

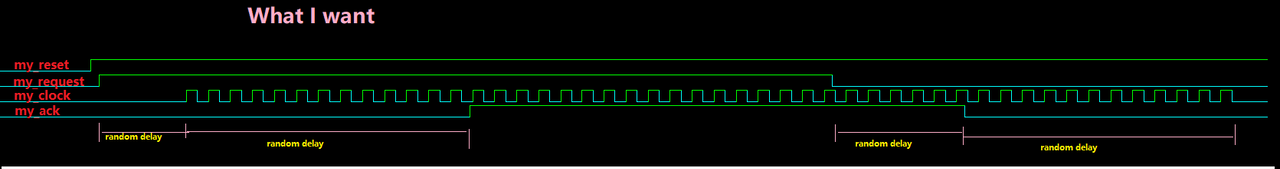

The specifications needed are as below:

- It works only when my_reset == 1.

- Delay between all the signals are totally random

- Signal have to meet the following sequences.

- my_request(rise) → random delay → my_clock(toggle) → random delay → my_ack(rise)

- my_request(fall) → random delay → my_ack(fall) → random delay → my_clock(stop toggle)

Please refer to the picture below.

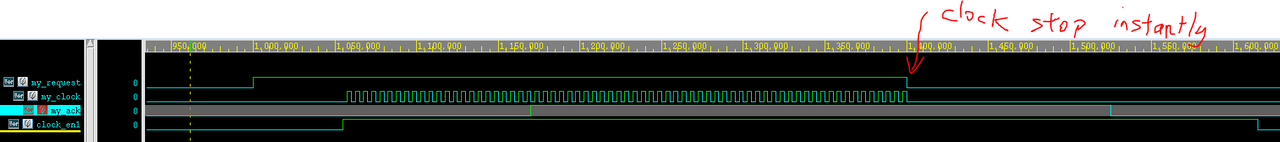

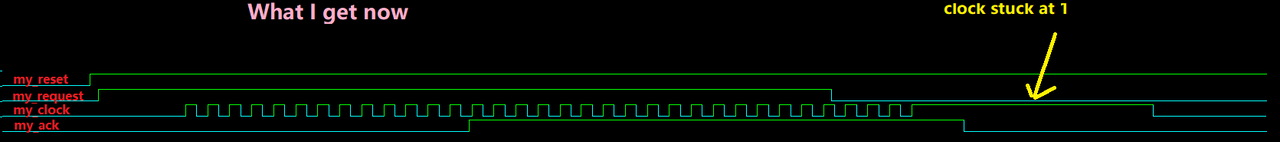

The result of my codes is in the picture below and it’s not meeting the specs.

Something has went wrong with the code and causing the clock stuck at 1.

Could you please comments, thanks.

my codes as below.

module clock_req_ack_handshake;

logic my_clock, my_request,my_reset,my_ack;

logic my_test_clock;

initial begin

my_test_clock = 0;

my_reset = 1;

my_ack = 0;

my_clock = 0;

my_request = 0;

#1us;

my_request = 1;

#400ns;

my_request = 0;

#1us;

$finish;

end

realtime my_test_clock_period = 5ns ;

always #(my_test_clock_period/2) my_test_clock = ~my_test_clock ;

realtime my_clk_random_delay_final ;

realtime my_clk_random_delay ;

realtime my_ack_random_delay ;

always @(posedge my_request) begin

my_clk_random_delay = $urandom_range(10,25)*my_test_clock_period;

my_ack_random_delay = $urandom_range(10,25)*my_test_clock_period;

my_clk_random_delay_final = my_clk_random_delay ; // clk delay comes after req, so ack delay is not required

#my_clk_random_delay;

#my_ack_random_delay;

my_ack = 1'b1;

end

always @(negedge my_request) begin

my_clk_random_delay = $urandom_range(10,25)*my_test_clock_period;

my_ack_random_delay = $urandom_range(10,25)*my_test_clock_period;

my_clk_random_delay_final = my_clk_random_delay + my_ack_random_delay ; // clk delay comes after ack, so ack delay is added in.

//#my_clk_random_delay; // ack comes first, clk delay comes after ack

#my_ack_random_delay;

my_ack = 1'b0;

end

always @(my_test_clock) begin

my_clock <= #my_clk_random_delay_final (my_test_clock && my_request && my_reset);

end

endmodule