In reply to syed taahir ahmed:

(($rose(ack) && request) || ($rose(ack) && $rose(request))

// By definition, $rose(a) is same as ! $past(a)!==1 && a

// Thus ((($rose(ack) && request) || ($rose(ack) && $rose(request)) is same as

((($rose(ack) && request) || ($rose(ack) && $past(request)==0 && request)

// The $past(request)==0 is not needed. Above is reduced to

($rose(ack) && request)

2. (##0 v_fail )

In the function, I used “pass”. The copy/paste copied the wrong testbench, sorry!

a_size0: assert(ldata != 0) else pass=0;

3. giving issues in capturing the data in queue ,

I don’t see how the pass or fail variable relates to the capture of data.

It’s irrelevant

4. still the property fail to capture when request and ack high at the same time.

// I dont get your issue.

property Data_handshake;

bit [255:0] v_data;

bit v_pass;

@(posedge clk)

($rose(request), gen_event(1)) |->

first_match(##[1:50] (($rose(ack) && request),

v_data=data, v_pass= t_check_data(1,1,v_data)))

##0 v_pass ##1 (!request && !ack) ##0 (1, gen_event(3)); // (!request && !ack);

endproperty

ap_Data_handshake: assert property (Data_handshake);

When ($rose(ack) && request) is true, you activate the function and pass to it the value of data stored in v_data prior to the function call. BTW, in this particular case, sice the time of the function call is the same as the time (or cycle) you capture the data, you can directly pass the data to the function without storing it into the local variable. That data will be sampled in the Preponed region.

5.

repeat(2) @(posedge clk); #200

request<=1; @(posedge clk) ack<=1; // #100 ack=1;

data <= 256'h9876_5430; //data 3

After the 2nd posedge clk, request==1, then at then posedge clk ack ==1 and data change value. At the next posedge clk, those values are sample in the Preponed region and $rose(ack) && request is true. The data is captured at that cycle.

I really do not understand your issues.

Updated testbench

module Data_unique;

reg clk = 1;

logic request,ack;

bit [255:0] data;

bit [255:0] out;

bit [255:0] q_data[$];

int dsize;

logic True = 1;

event e1, e2, e3;

assign dsize=q_data.size;

function automatic void gen_event(int a);

if(a==1) -> e1;

if(a==2) -> e2;

if(a==3) -> e3;

endfunction : gen_event

always #50 clk = ~clk;

initial

begin

$dumpfile("dump.vcd"); $dumpvars;

request<=0; ack<=0; data <= 0; // 1; // <<<<********NEW

repeat(2) @(posedge clk); //#200

request<=1; @(posedge clk) ack<=0; //#100 ack=0; // request started

repeat(5) @(posedge clk); // #500

@(posedge clk) ack<=1; //#100 ack=1; // ack and data

data <= 256'habcd_5555;//data 1

// data = 0; // error condition when data =0

@(posedge clk); //#100

request<=0; ack<=0;data<=0;

repeat(2) @(posedge clk); // #200

request<=1; repeat(2) ack<= 1; // #200 ack=1;

data <= 256'h1234_5678; // data2

@(posedge clk); // #100

request<=0; ack<=0;data<=0;

repeat(2) @(posedge clk); #200

request<=1; @(posedge clk) ack<=1; // #100 ack=1;

data <= 256'h9876_5430; //data 3

// data = 256'h1234_5678; //same data causes violation

@(posedge clk); // #100

request<=0; ack<=0; data<=0;

repeat(3) @(posedge clk); // #300

request<= 1; repeat(3) ack<=1; // #300 ack=1; //

data <= 256'hdcba_5555; // data 4

//data = 256'h9876_5430; //same data causes violation

@(posedge clk); // #100

request<=0; ack<=0;data <=0;

repeat(5) @(posedge clk); // #500

$finish;

end

function automatic t_check_data(bit ack_sync,bit request_sync, bit [255:0] ldata);

automatic bit pass=1;

->e2;

// @(posedge clk)

if(request_sync && ack_sync ==True) begin : is_valid

if (q_data.size == 0)begin

q_data.push_back(ldata);

a_size0: assert(ldata != 0) else pass=0;

// $error("Data should be non zero\n");

end

else begin

out = ldata;

foreach(q_data[i]) begin

assert(out !== q_data[i]) else pass=0;

end

q_data.push_back(ldata);

end

$display("@ %t out_data = %0h q_data=%0p", $time,out,q_data);

end

// @(posedge clk) a_handshake: assert(!request && !ack);

return pass;

// end

endfunction

/* property Data_handshake_V0;

@(posedge clk)

($rose(request)) |-> ##[1:50] (($rose(ack) && request) , t_check_data(1,1))

##1 (!request && !ack);

endproperty */

/* property Data_handshake;

bit [255:0] v_data;

bit v_fail;

@(posedge clk)

$rose(request) |->

first_match(##[1:50] ((($rose(ack) && request) || ($rose(ack) && $rose(request))),v_data=data,t_check_data(1,1,v_data))

##1 (!request && !ack)); // (!request && !ack);

endproperty

ap_Data_handshake: assert property (Data_handshake); */

// As From

property Data_handshake;

bit [255:0] v_data;

bit v_pass;

@(posedge clk)

($rose(request), gen_event(1)) |->

first_match(##[1:50] (($rose(ack) && request),

v_data=data, v_pass= t_check_data(1,1,v_data)))

##0 v_pass ##1 (!request && !ack) ##0 (1, gen_event(3)); // (!request && !ack);

endproperty

ap_Data_handshake: assert property (Data_handshake);

property Data_handshake_option2;

bit [255:0] v_data;

bit v_pass;

@(posedge clk)

($rose(request), gen_event(1)) |->

first_match(##[1:50] (($rose(ack) && request),

//v_data=data,

v_pass= t_check_data(1,1,data)))

##0 v_pass ##1 (!request && !ack) ##0 (1, gen_event(3)); // (!request && !ack);

endproperty

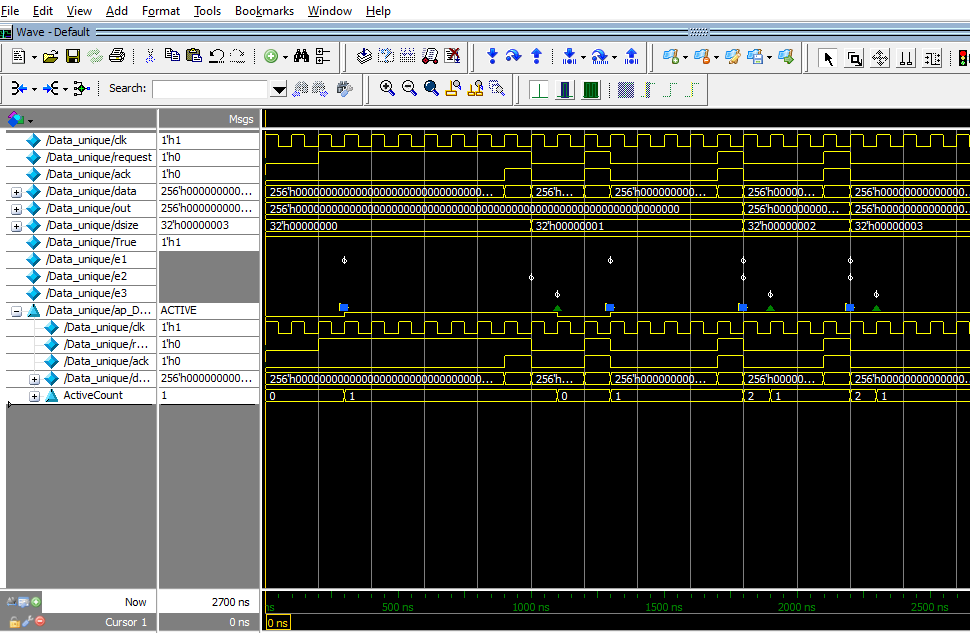

// sim results http://systemverilog.us/vf/data_unique2.png

# @ 1000 out_data = 0 q_data=2882360661

# @ 1800 out_data = 98765430 q_data=2882360661 2557891632

# @ 2200 out_data = dcba5555 q_data=2882360661 2557891632 3703199061

endmodule

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact Home - My cvcblr

- SVA Alternative for Complex Assertions

https://verificationacademy.com/news/verification-horizons-march-2018-issue

- SVA: Package for dynamic and range delays and repeats - SystemVerilog - Verification Academy

- SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment