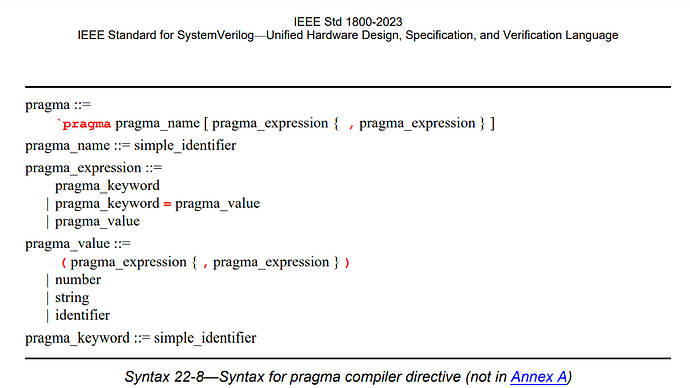

The `pragma directive is a structured specification that alters interpretation of the SystemVerilog source.Following is the syntax which is provided in the SystemVerilog LRM[IEEE std 1800-2023] for pragma compiler directive:

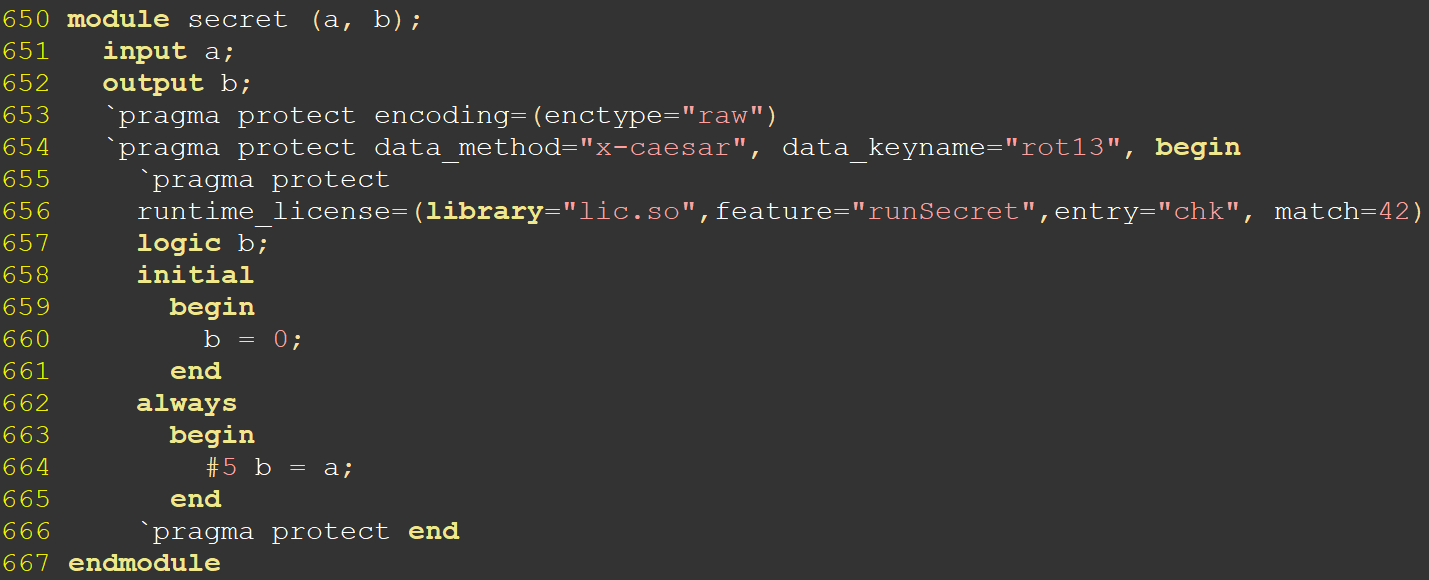

I am trying to do the encryption example provided in section 34.3.1 of LRM.

The above code is not working how it is supposed to, kindly help me understand it. Also I observed that the syntax for pragma is not matching with the example in Section 34.3.1.

Another example I have tried is to encrypt the RTL code of D-flip flop using `pragma compiler directive, which is again not working.

module RisingEdge_DFlipFlop(input D,clk,output reg Q);

`pragma protect begin

always @(posedge clk) begin

Q <= D;

end

`pragma protect end

endmodule