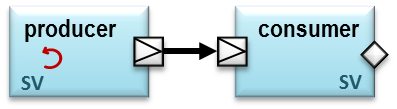

UVMC Connection Example - Native SV to SV

This example reviews how to make a local, native TLM connections between two UVM components in pure SystemVerilog testbench. UVMC is not used. The UVMC Connection Example - UVMC-based SV to SV uses UVMC to make the same local SV connection.

The sv_main top-level module below creates and starts the SV portion of this example. It does the following:

- Creates an instance of a producer component

- Connects the producer’s out port to the consumer’s in port using the native UVM TLM connection.

- Calls run_test to start UVM simulation

TLM connections are normally made in the connect_phase callback of a UVM component. This example does not show that for sake of highlighting the connect functionality.

import uvm_pkg::*;

`include "producer.sv"

`include "consumer.sv"

module sv_main;

producer prod = new("prod");

consumer cons = new("cons");

initial begin

prod.out.connect(cons.in);

run_test();

end

endmoduleSummary

| UVMC Connection Example - Native SV to SV | |

| This example reviews how to make a local, native TLM connections between two UVM components in pure SystemVerilog testbench. |