I am planning to write a ACE protocol UVM Test bench. Can somebody review this and see if it is okay? Also if somebody has written ACE protocol, can somebody share the test plan?

- Have one ACE Interface

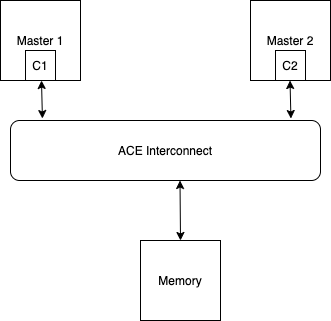

- Master 1 and Master 2 are UVM components and they have cache 1 and cache 2 inside it. If there are transactions coming out from Master 1 for example, it will be checked in Cache 1 and then sent to interconnect.

- Interconnect here is an active driver which checks for transactions from either Masters or Memory controller and drives on the bus.