In reply to Have_A_Doubt:

If you have to worry about the event regions to correctly trigger a covergroup, then something is wrong in the methodology or approach. On

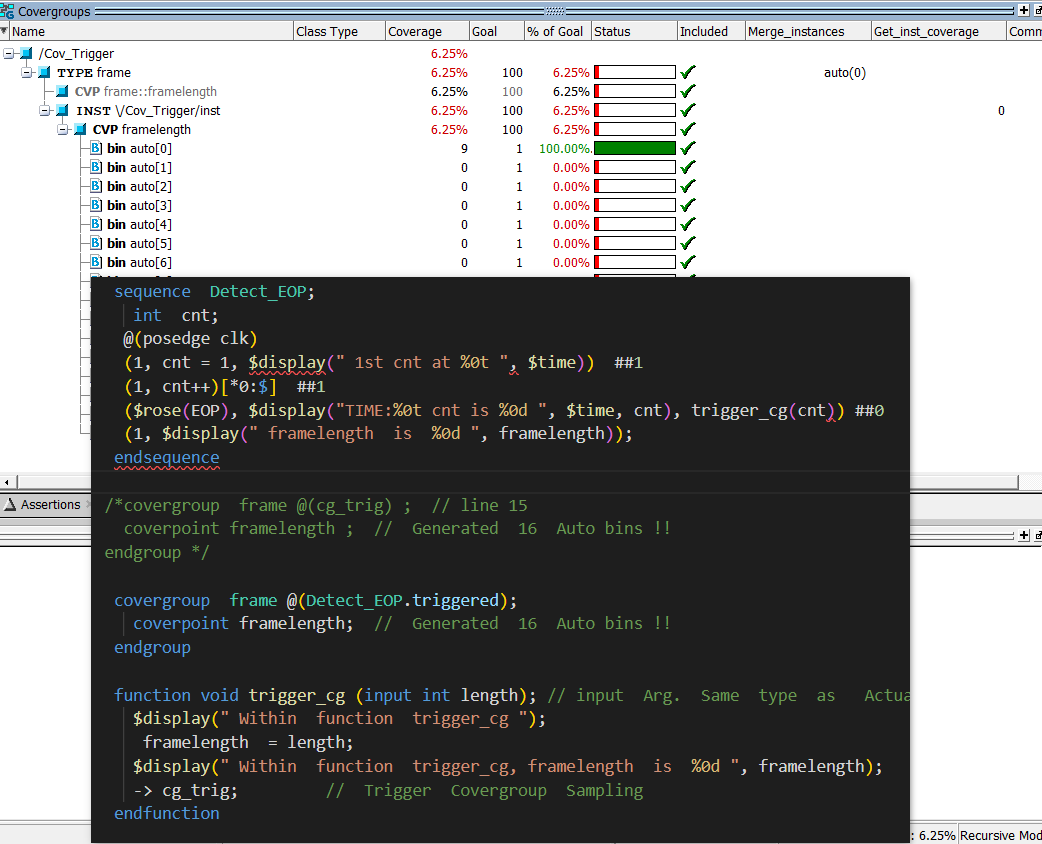

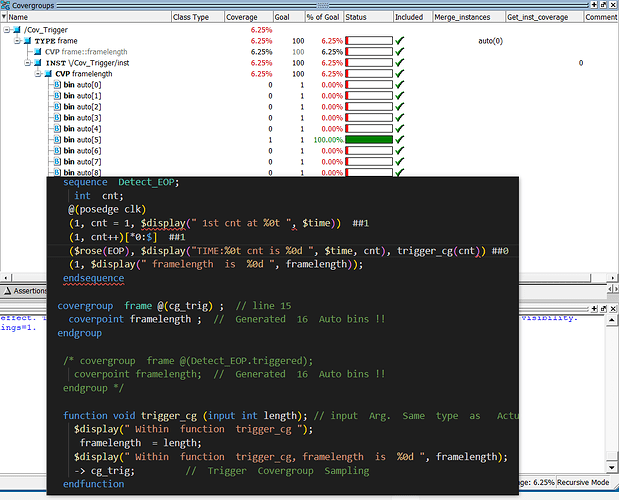

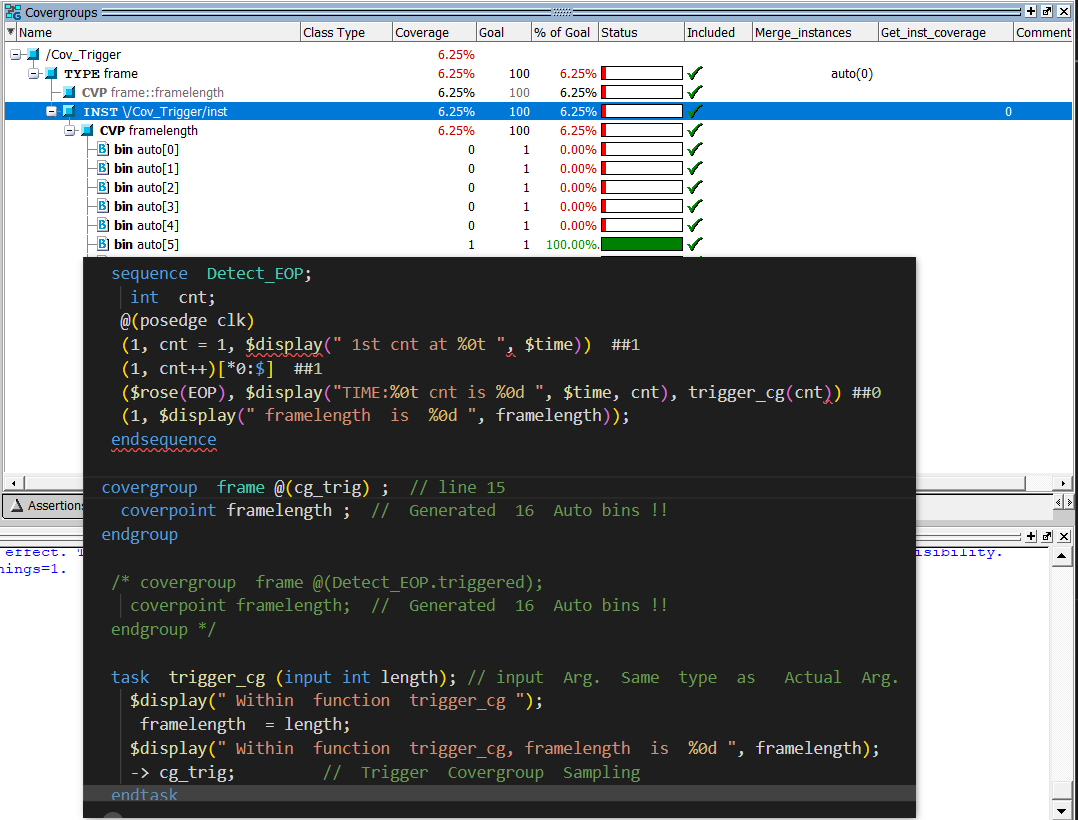

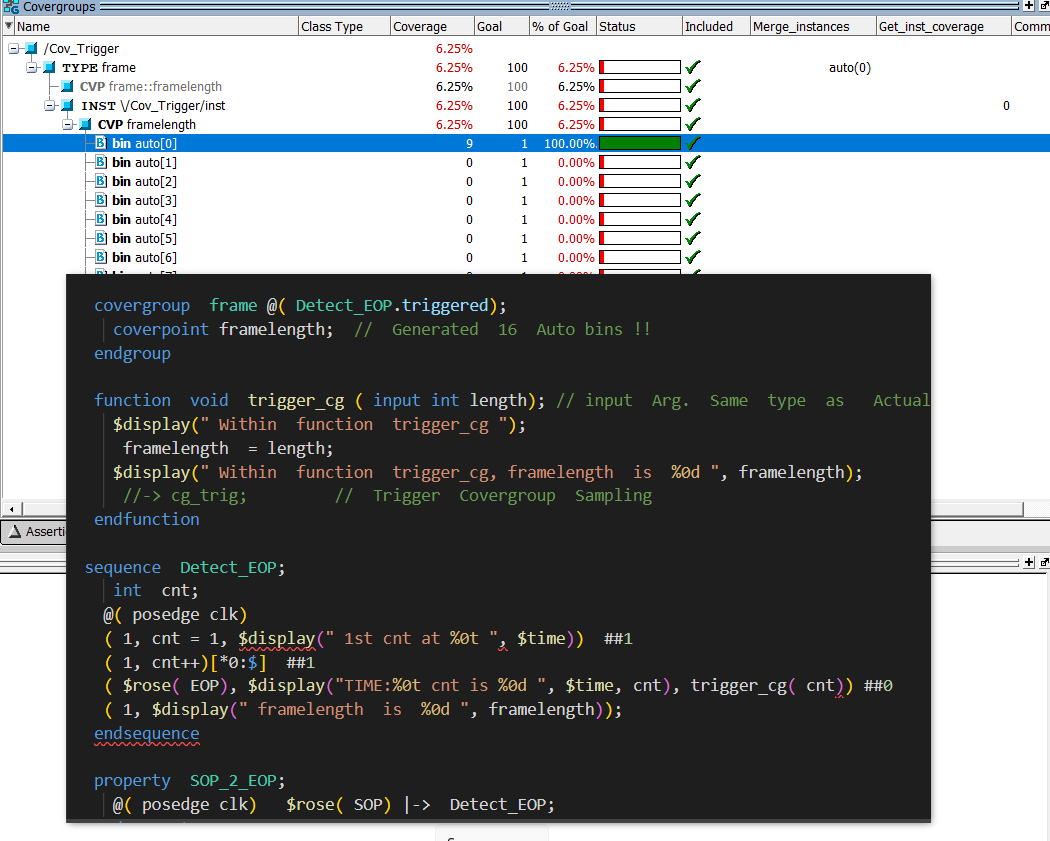

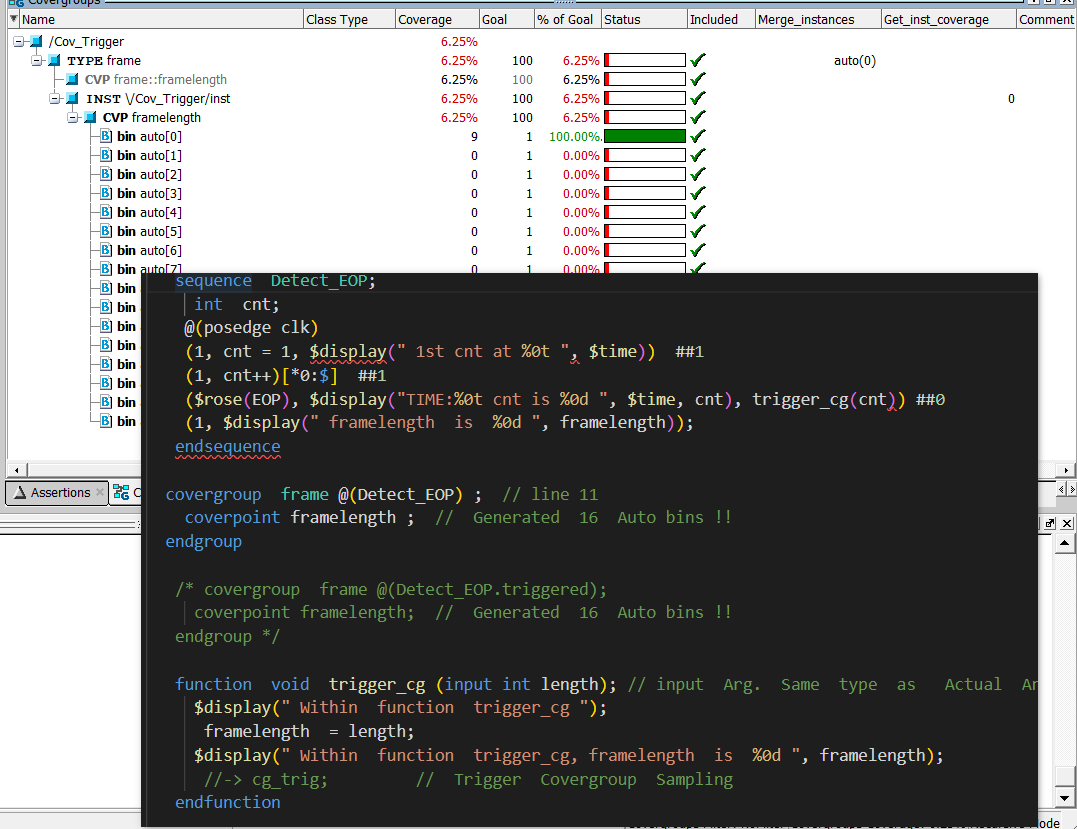

(1) Via @( Detect_EOP ) some tools correctly sample auto[5] while others still cover auto[0] unfortunately.

sequence Detect_EOP;

int cnt;

@(posedge clk)

(1, cnt = 1) ##1 (1, cnt++)[*0:$] ##1

($rose(EOP), trigger_cg(cnt));

endsequence

function void trigger_cg (input int length);

framelength = length;

// -> cg_trig; // Trigger Covergroup Sampling

endfunction

covergroup GOOD_frame @(Detect_EOP); // GOOD use of sequence_name for the trigger

coverpoint framelength; // Generated 16 Auto bins !!

endgroup

1800: “The subroutines are scheduled in the Reactive region, like an action block.”

The way I see this is that the function is called in the Reactive region.

Thus at the endpoint of the assertion that uses that sequence, the triggers the

covergroup GOOD_frame @(Detect_EOP) occurs in the Observed region because of the @(Detect_EOP).

Following that trigger the function is called, and that function updates the framelength.

Thus, the value of the capture framelength is 0, set at the declaration by default.

An alternative would be calling sample() function from the subroutine ( instead of triggering the event in subroutine )

This would mean there is no sampling event defined for covergroup i.e covergroup frame ;

Yes, that is a better approach.

I did this in my paper SVA for statistical analysis of a weighted work-conserving prioritized round-robin arbiter.

https://verificationacademy.com/forums/coverage/sva-statistical-analysis-weighted-work-conserving-prioritized-round-robin-arbiter.

function automatic void setdelay(int delay, k);

req2grant[k]=delay;

cg_inst.sample(); // for covergroup

endfunction

property p_req2grant_delay; // Used to count the cycle delays

// from each req to each corresponding grant

// At the grant, the function call provides the sampling of the covergroup

int delay;

@(posedge clk) ($rose(req[j]), delay = 1) |-> ##1

(!sc_grnt[j], delay++)[*0:$] ##1

(sc_grnt[j], setdelay(delay, j));

endproperty

1800 addressing the triggering of the covergroup. I would hate to have to think about the inner-workings of SV regions to get the trigger correctly. Sorry!

// 17.6 Covergroups in checkers

bit [3:0] opcode_d1;

always_ff @(posedge clk) opcode_d1 <= opcode;

covergroup cg_op;

cp_op : coverpoint opcode_d1;

endgroup:

cg_op cg_op_1 = new();

sequence op_accept;

@(posedge clk) vld_1 ##1

(vld_2, cg_op_1.sample());

endsequence cover property (op_accept);

/* endchecker In this example, the coverpoint cp_op refers to the checker

variable opcode_d1 directly. It is triggered by a call to the default

sample() method from a sequence match item. This function call occurs

in the Reactive region, while nonblocking assignments to checker variables

will occur in the Re-NBA region. As a result, the covergroup will sample

the old value of the checker variable opcode_d1. */

//---------------------------

// It is also possible to define a custom sample() method for a

// covergroup (see 19.8.1 ). The following is an example of this: */

checker op_test (logic clk, vld_1, vld_2, logic [3:0] opcode);

bit [3:0] opcode_d1;

always_ff @(posedge clk) opcode_d1 <= opcode;

covergroup cg_op with function sample(bit [3:0] opcode_d1);

cp_op : coverpoint opcode_d1;

endgroup: cg_op

cg_op cg_op_1 = new();

sequence op_accept; @(posedge clk) vld_1 ##1

(vld_2, cg_op_1.sample(opcode_d1));

endsequence

cover property (op_accept);

endchecker

/* In this example, a custom sample() method has been defined for the

covergroup cg_op, and the coverpoint cp_op references the formal argument

of the custom sample() method. This custom method will be called in the

Reactive region upon a sequence match, but the sampled value of

the sequential checker variable opcode_d1 will be passed to the sample()

function. As a result, the covergroup will sample the value from

the Preponed region. */