when to cover property over cover point? explain with an example?

In reply to sh88:

From my SVA book:

Loosely speaking, a cover point is a condition that must be reached. In simulation, cover points the cumulative coverage of tests. In formal verification, cover points ensure that certain properties and sequences are reachable under the constraints. A cover point is described with a cover property or cover sequence assertion statement. If a cover point fails in simulation, it is either because it cannot be reached, or because the stimulus vector was not complete enough to reach it. In formal verification, if a cover point fails, it is because either it cannot possibly be reached because of the RTL, or the assumptions are over restrictive, thus preventing the tool to generate a trace.

A covergroup can contain one or more coverage points. They are used in simulation but not in formal verification. For formal verification, you would need to use the SVA cover, and those are cover sequence and cover property, and immediate cover.

I Address that in my SVA book

I extracted the 5 pertinent pages for you here.

A cover property will be flagged by a simulation as covered if the property is true. The cover property never fails. Actually, all cover statements never fail, they just identify if the item being covered (sequence, expression, property) was exercised.

Assertions automatically provide coverage, but they also identify failures.

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact Home - My cvcblr

** SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

…

- SVA Package: Dynamic and range delays and repeats SVA: Package for dynamic and range delays and repeats | Verification Academy

- Free books: Component Design by Example FREE BOOK: Component Design by Example … A Step-by-Step Process Using VHDL with UART as Vehicle | Verification Academy

Real Chip Design and Verification Using Verilog and VHDL($3) Amazon.com - Papers:

- SVA Alternative for Complex Assertions

Verification Horizons - March 2018 Issue | Verification Academy - SVA in a UVM Class-based Environment

SVA in a UVM Class-based Environment | Verification Horizons | Verification Academy - Understanding the SVA Engine,

Verification Horizons - July 2020 | Verification Academy

In reply to ben@SystemVerilog.us:

Hi Ben,

In formal verification, when do we need to use cover property and assume property?

If only using assume property, is it wrong?

Thanks !

In reply to peter:

In formal verification, when do we need to use cover property and assume property?

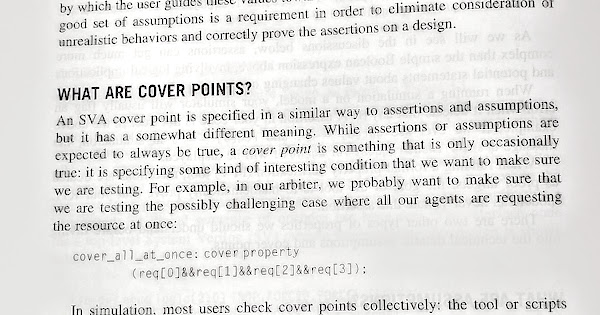

Erik Seligmnan, author of Formal Verification, an Essential toolkit for Modern VLSO Design explains this difference very well. I know Eric, and I hope he does not mind that I am sharing a photo of that page that addresses you topic.

I strongly suggest that you or your company buy this book if your work involves assertions and/or formal verification. https://www.amazon.com/Formal-Verification-Essential-Toolkit-Modern/dp/0128007273