Hi!

For some reasons, I have module that can’t be connected using modport:

module test_int (

// Synchro signal and reset

input logic ACLK,

input logic ARESETN,

// Interface S_AXIS_DATA

input logic S_AXIS_DATA_TVALID,

output logic S_AXIS_DATA_TREADY,

input logic S_AXIS_DATA_TLAST,

input logic [31:0] S_AXIS_DATA_TDATA,

input logic [7:0] S_AXIS_DATA_TUSER,

// Interface M_AXIS_DATA

output logic M_AXIS_DATA_TVALID,

input logic M_AXIS_DATA_TREADY,

output logic M_AXIS_DATA_TLAST,

output logic [31:0] M_AXIS_DATA_TDATA,

output logic [7:0] M_AXIS_DATA_TUSER

);

I also have a SLAVE and MASTER interfaces:

interface com_tb_int_in #(

parameter TDATA_WIDTH = 32,

parameter TUSER_WIDTH = 32

)

(

input logic ACLK,

input logic ARESETN

);

logic S_AXIS_TVALID = 0;

logic S_AXIS_TREADY;

logic S_AXIS_TLAST = 0;

logic [TDATA_WIDTH-1:0] S_AXIS_TDATA;

logic [TUSER_WIDTH-1:0] S_AXIS_TUSER;

clocking cb @(posedge ACLK);

input S_AXIS_TREADY;

output S_AXIS_TVALID;

output S_AXIS_TLAST;

output S_AXIS_TDATA;

output S_AXIS_TUSER;

endclocking

endinterface

interface com_tb_int_out #(

parameter int TDATA_WIDTH = 32,

parameter int TUSER_WIDTH = 32

)

(

input logic ACLK,

input logic ARESETN

);

logic M_AXIS_TVALID;

logic M_AXIS_TREADY = 0;

logic M_AXIS_TLAST;

logic [TDATA_WIDTH-1:0] M_AXIS_TDATA;

logic [TUSER_WIDTH-1:0] M_AXIS_TUSER;

clocking cb @(posedge ACLK);

input M_AXIS_TVALID;

output M_AXIS_TREADY;

input M_AXIS_TLAST;

input M_AXIS_TDATA;

input M_AXIS_TUSER;

endclocking

endinterface

Can I connect DUT and TB like this:

module test_int_tb (

input logic ACLK,

input logic ARESETN

);

// S_AXIS_DATA

com_tb_int_in #(

.TDATA_WIDTH (32),

.TUSER_WIDTH (8)

) com_tb_int_in_data_inst (

.ACLK (ACLK),

.ARESETN (ARESETN)

);

// M_AXIS_DATA

com_tb_int_out #(

.TDATA_WIDTH (32),

.TUSER_WIDTH (8)

) com_tb_int_out_inst (

.ACLK (ACLK),

.ARESETN (ARESETN)

);

// module test_int instantiation

test_int test_int_inst (

// Synchro signals and reset

.ACLK (ACLK),

.ARESETN (ARESETN),

// Interface S_AXIS_DATA

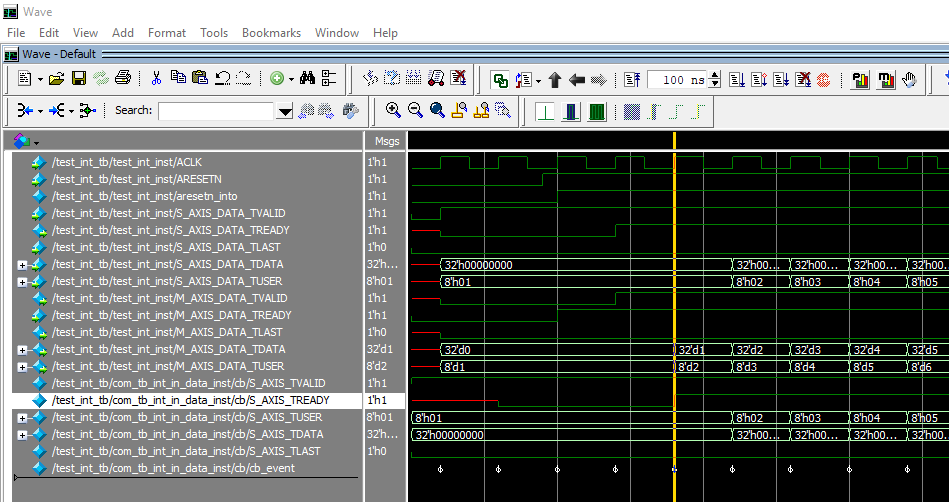

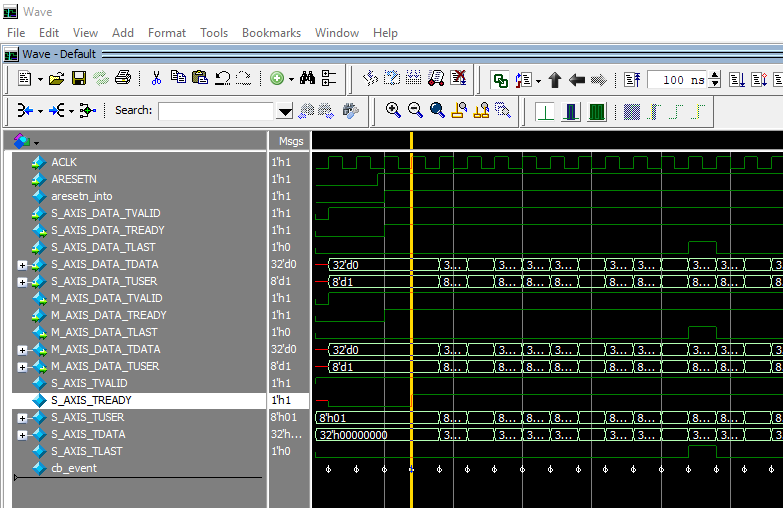

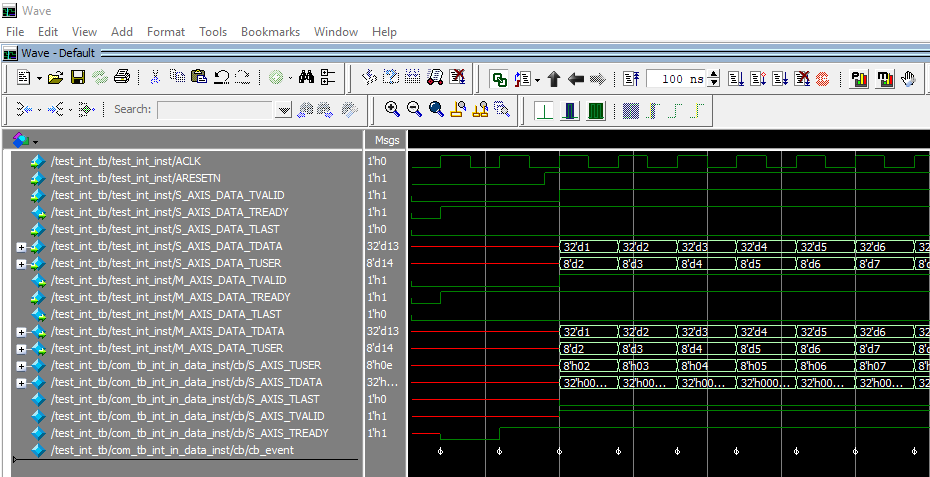

.S_AXIS_DATA_TVALID (com_tb_int_in_data_inst.cb.S_AXIS_TVALID),

.S_AXIS_DATA_TREADY (com_tb_int_in_data_inst.cb.S_AXIS_TREADY),

.S_AXIS_DATA_TLAST (com_tb_int_in_data_inst.cb.S_AXIS_TLAST),

.S_AXIS_DATA_TDATA (com_tb_int_in_data_inst.cb.S_AXIS_TDATA),

.S_AXIS_DATA_TUSER (com_tb_int_in_data_inst.cb.S_AXIS_TUSER),

// Interface M_AXIS_DATA

.M_AXIS_DATA_TVALID (com_tb_int_out_inst.cb.M_AXIS_TVALID),

.M_AXIS_DATA_TLAST (com_tb_int_out_inst.cb.M_AXIS_TLAST),

.M_AXIS_DATA_TREADY (com_tb_int_out_inst.cb.M_AXIS_TREADY),

.M_AXIS_DATA_TDATA (com_tb_int_out_inst.cb.M_AXIS_TDATA),

.M_AXIS_DATA_TUSER (com_tb_int_out_inst.cb.M_AXIS_TUSER)

);

endmodule